design of booth multiplier

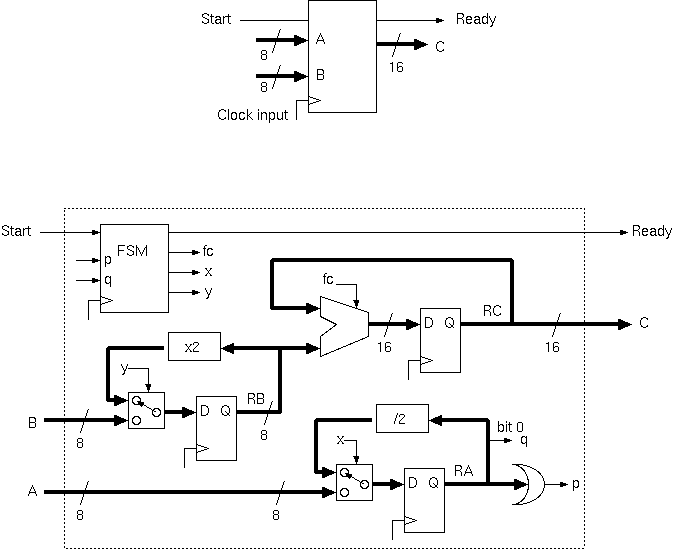

The overall booth’s array multiplier for 6-bits is shown in figure 2. this multiplier is capable of performing sign multiplication without any extra hardware. the control signals are generated from the control blocks (cb). total 18 sbs are used in this design. figure 2: booth’s array multiplier for two 6-bit operands. Multiplication method have been proposed in [4-7]. in [8], two new approximate 4-2 compressors have been proposed for designing an approximate array multiplier. this design is a truncated scheme, because it overcomes most of the accuracy and correctness issues due to truncation. the wallace-booth multiplier design is the most popular. Section 1.2 design of a radix-4 booth multiplier using verilog. booth’s multiplier can be either a sequential circuit, where each partial product is generated and accumulated in one clock cycle, or it can be purely combinational, where all the partial products are generated in parallel. our objective is to do a combinational multiplier..

design of booth multiplier